参数:

|

Applications

|

GPIO

|

|

Bits (#)

|

1

|

|

Configuration

|

1 Ch A to B; 0 Ch B to A

|

|

Vout (Min) (V)

|

1.1

|

|

Vout (Max) (V)

|

5.5

|

|

IOH (Max) (mA)

|

32

|

|

IOL (Max) (mA)

|

-32

|

|

Rating

|

Catalog

|

封装 | 引脚 | 尺寸:

|

SOT-SC70 (DCK)

|

5

|

4 mm² 2 x 2.1

|

特性:

- Fully configurable dual-rail design allows each port to operate from 1.1 V to 5.5 V

- Robust, glitch-free power supply sequencing

- Up to 420-Mbps support for 3.3 V to 5.0 V

- Schmitt-trigger inputs allow for slow or noisy inputs

- Input with integrated dynamic pull-down resistors help reduce external component count

- High drive strength (up to 32 mA at 5 V)

- Low power consumption

- 3-µA maximum (25°C)

- 6-µA maximum (–40°C to 125°C)

- VCC isolation and Vcc disconnect (Ioff-float) feature

- If either VCC supply is < 100 mV or disconnected, all I/O’s get pulled-down and then become high-impedance

- Overvoltage tolerant inputs accept voltages up to 5.5 V regardless of supply voltage.

- Ioff supports partial-power-down mode operation

- Operating temperature from –40°C to +125°C

- Latch-up performance exceeds 100 mA per JESD 78, class II

- ESD protection exceeds JESD 22

- 4000-V human-body model

- 1000-V charged-device model

说明:

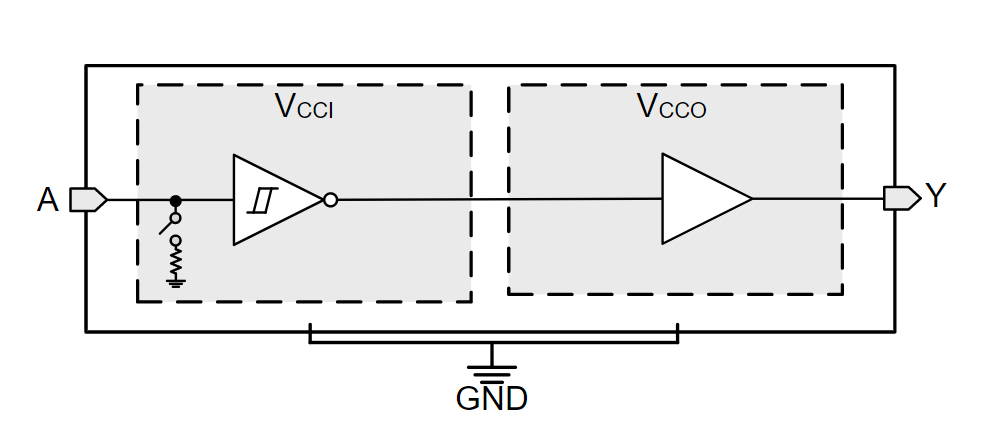

The SN74LXC1T14 is a single bit, dual-supply inverting voltage level translation device with Schmitt-trigger input. The input pin A is referenced to VCCI logic levels, and output pin Y is referenced to VCCO logic levels. The input pin A is able to accept voltages ranging from 1.1 V to 5.5 V and can be connected directly to VCCI or GND. See Device Functional Modes for a summary of the operation of the logic.

This device ensures low power consumption and is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs when the device is powered down. This inhibits current backflow into the device which prevents damage to the device.

图片展示: